摘 要

芯片的生产与光刻机的精度息息相关,除了光刻机的精度外,多次曝光工艺也可以进一步提高芯片的制程,本文主要介绍如何采用28 nm DUV光刻机来制造7 nm工艺要求的芯片。

关键词:光刻机;制程;芯片

五代光刻机是如何发展的?

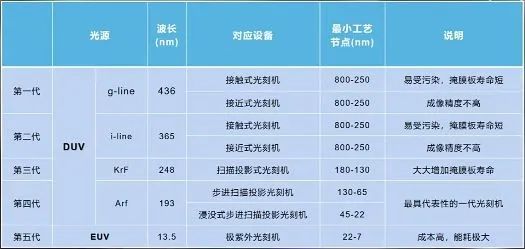

各种手机、电脑的CPU芯片都是由光刻机生产制造的,一般来说光刻机的精度决定了芯片的先进程度,即运算速度和处理能力[1]。从最初代的光刻机到目前最先进的EUV光刻机,依据采用激光光源波长的不同大概划分为五代。第一代采用水银蒸汽灯的g线波长,对应436 nm紫外光;第二代采用水银蒸汽灯的i线波长,对应365 nm紫外光;第三代采用KrF的248 nm紫外光;第四代采用ArF的193 nm紫外光;第五代,极紫外光刻机(EUV)采用13.5 nm的极紫外光。如图所示,随着光刻机的发展,光刻机光源波长不断降低,已经能够实现7 nm的最小工艺节点[2]。

图1 五代光刻机的光源及波长(来自网络)

从芯片制造技术来看,光刻机起到重要的转移作用,即将电路图转移到晶圆上。为了保证电路图的精确转移和在晶圆上完全复刻,需要把光源系统、光学系统、物镜系统和平台系统进行系统整合[3]。目前的光刻机都是由这些子系统来组成,每个子系统都发挥着不同的作用。任何一个子系统的设计、制造都是该领域的尖端技术,这也是光刻机制造的困难之处。借助上述子系统的运行和配合,光刻机可以实现纳米级别的电路转移和处理。光刻机的精度和稳定性,直接影响芯片的良率和结构完整性。然而,芯片技术开发和芯片大规模量产属于两个概念。这就导致芯片代工企业和芯片设计企业会充分考虑各种因素,来决定采用何种工艺生产芯片。例如,就工艺而言,ArF 193 nm波长DUV光刻机能够实现7 nm制程芯片的生产。这涉及到一个重要的问题——制程[4]。

什么是“制程”?

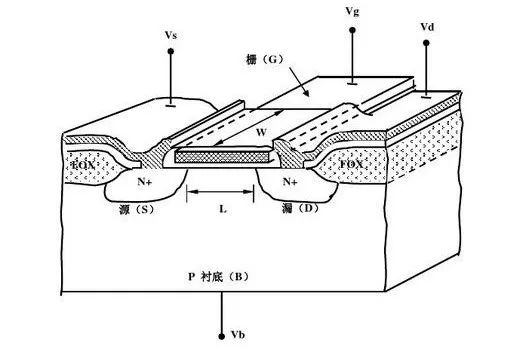

晶体管结构中,电流会从源极(source)流入漏极(drain),栅极(gate)相当于闸门,负责控制源极和漏极之间的通断。栅极的宽度决定了电流通过时的损耗,栅极越宽,电流经过的距离越长,损耗越大,表现为芯片的发热和性能降低。栅极越窄,损耗越小,芯片的性能也越好。栅极的最小宽度就是制程。从这个角度来说,较小的制程可以有效提升芯片的性能。但栅极间的距离也不是无限减小的,目前栅极间的7 nm间距基本上接近物理极限。距离再减小,栅极间会出现“电流泄漏”,导致电路运行失效、芯片失效等问题。

图2 源极、漏极和栅极的示意图(来自网络)

光刻机的制程工艺是怎样的?

介绍完制程的概念,接下来介绍制程的具体实现过程。特别是,如何用最小节点为28 nm的光刻机来生产7 nm制程的芯片。这涉及到第二个问题——工艺。目前只有台积电和三星可以实现7 nm制程的大规模量产。三星采用EUV光刻机来实现7 nm制程;台积电先是使用DUV光刻机实现了7 nm制程,又采用EUV光刻机实现了7 nm工艺。这就说明,DUV和EUV都可以实现7 nm制程。下面介绍采用DUV光刻机制造7 nm制程芯片的过程。

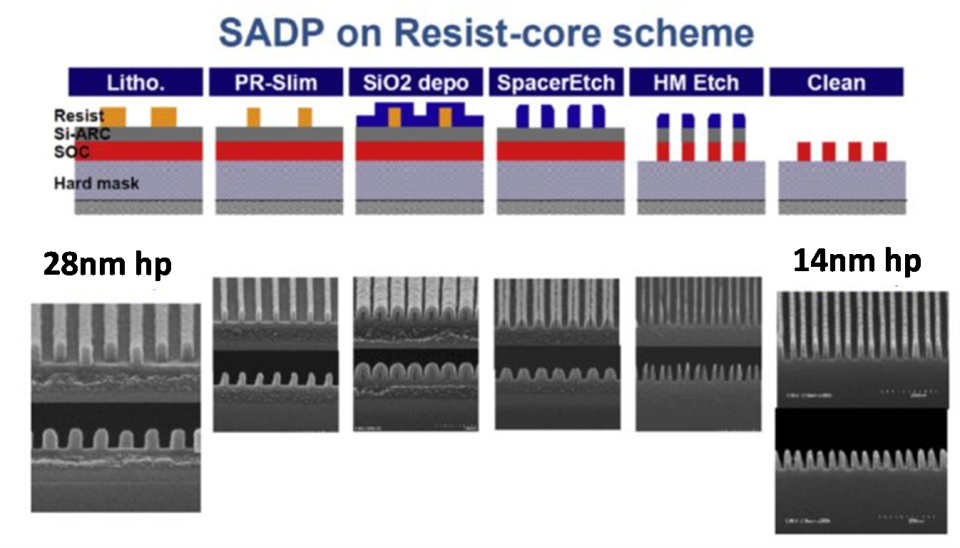

光刻机进入第四代后,最小工艺节点为28 nm,要想继续提高制程,依靠单次曝光已经无法做到,产业界开始采用多次曝光/刻蚀来实现缩小制程[5]。其中,最关键的两种工艺是双重曝光技术(double exposure,DE)和自对准双重成像技术(self aligned double patterning,SADP)。双重曝光采用前后曝光不同图形(叠加)的办法来实现更小制程(更高分辨率)。这种方法的优点是可以实现更高精度,缺点是增加了成本和工艺,且对叠加精度要求较高。相比之下,SADP技术则容易得多,同时可以实现精度提高一倍,DUV光刻机结合SADP可以实现14 nm的最小节点。

图3 阿斯麦DUV光刻机(来自网络)

SADP技术具体的操作是什么?

1)首先在有硬掩模版的晶圆上使用光刻工艺一次,得到28 nm的光刻胶图形;

2)通过刻蚀工艺,将光刻胶图形宽度减小一半;

3)在光刻胶上沉积二氧化硅薄膜;

4)分别将表层的二氧化硅薄膜刻蚀掉,露出薄膜下面的光刻胶;再使用另外的刻蚀溶剂只将光刻胶刻蚀除去,留下光刻胶两侧侧壁作为新模板,相比开始的28 nm间距,目前为14 nm间距;

5)将上述侧壁作为掩模版,向下进一步刻蚀,将图形转移到硬掩模版上;

6)最后,将硬掩模版上的表层二氧化硅清洗掉,就可以得到14 nm间距的图形了,也就是实现了14 nm制程。

图4 SADP技术原理(来自网络)

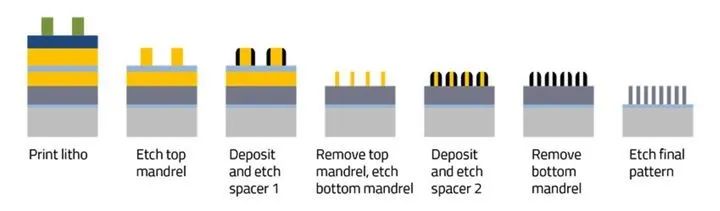

自动对准四重成像技术的应用

使用DUV光刻机实现14 nm制程,SADP是一个有效的方法。但这种方式适用于图形相对简单的电路。对于复杂的电路,还需要采用合并-拆分的方式来实现。目前距离我们7 nm的目标还有一段距离,实现方法就是自动对准四重成像技术(self aligned quadruple patterning,SAQP)。与SADP相似,在前面14 nm间距的基础上,再使用一次SADP技术,就可以实现间距(制程)的进一步缩小,得到我们想要的7 nm制程[6]。

图5 SAQP技术原理(来自网络)

以上就是采用DUV光刻机,结合SADP技术获得7 nm制程的方法。使用EUV光刻机则不用如此麻烦。EUV光刻机的光源为13.5 nm的极紫外光,单次曝光就可以达到13 nm的分辨率,要得到7 nm制程芯片,使用极限特征尺寸单次曝光即可。结合SADP/SAQP技术,EUV光刻机得以实现5 nm/3 nm等制程。需要指出的是,DUV和EUV都可以实现7 nm的制程,但EUV光刻机的制备流程更少,图形分辨率也更高,可以有效提高芯片的良率。采用DUV技术可以实现7 nm工艺,倘若要大量生产,中间的工艺次数和复杂程度大大增加,对于芯片制造企业来讲,基本不具备经济效益。

总 结

光刻机已经发展到第五代,但我国的高端光刻机设备及相关技术仍受制于人。通过对生产技术的进一步开发,在一定程度上可以实现更小的制程,可以有效利用国内的芯片产能,特别是国内的28 nm光刻机产能。结合其他降低成本的技术,还可以有效缩小和先进芯片厂商的差距。

暂无评论

发表评论